導入

Z80000 は、 1986 年に Zilog 社が発売した32 ビットマイクロプロセッサです。

建築要素

Z80000 アーキテクチャのサブセットは、1979 年には16 ビットZ8000 プロセッサに実装されており、Z8030 シリアル通信コントローラや Z8016 DMA コントローラなど、Z8000 用に設計された周辺機器を Z80000 で使用できるようになりました。 Z80000 は、Z8000 用にコンパイルされたコードを実行できましたが、Zilog Z80 からのコードは実行できなかったため、Intel のx86アーキテクチャと互換性がありませんでした。シリコンで驚くほど経済的 (トランジスタ数はわずか 91,000 個) で、概念的にはインテルの競合他社よりもはるかに先を行っていましたが、完成の遅れによりマーケティングは完全に失敗しました (1983 年に発表され、1986 年以降になるまで市場に投入されませんでした)。特に、多数のバグを抱えて時期尚早に販売された前世代の Z8000 の信頼性を高めるのが困難でした。

Z80000 の高度な機能には次のものが含まれます。

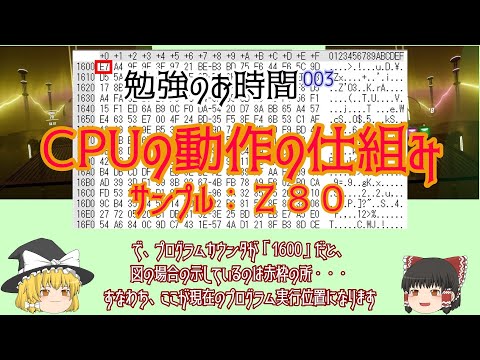

- 命令の実行は 6 つのレベルで完全にパイプライン化され、回路のハードワイヤード リソースの使用において一定の並列処理が可能になりました。

- もし:

- 序数カウンタ(命令ポインタ)のインクリメント

- 統合キャッシュタグの比較

- ID :

- 命令キャッシュからの読み取り

- マイクロ命令の生成

- AC :

- 論理アドレスの計算

- アドレス変換キャッシュ ラベルの比較 (変換ルックアサイドバッファ)

- アドレス変換キャッシュからの物理アドレスの決定

- の:

- 埋め込みキャッシュラベルの比較

- 隠しデータの読み取り

- 元:

- レジスタの読み取り

- 算術および論理計算

- レジスタの書き込み

- 骨:

- Z8000 と同様に、このプロセッサは、アプリケーションをオペレーティング システム機能から分離するために、システム モードと通常モード( F & C Wのビット#14 によって制御される) で動作できます。システム モードで実行されるコードのみが、入出力関数と制御レジスタ、およびシステム モードのメモリ空間にアクセスできます。システム モードと通常モード用の個別のスタックにより、アーキテクチャの安全性がさらに高まりました。

- Z80000 は32 ビット論理アドレスを使用し、最大4 GiBの物理メモリをアドレス指定できました。論理アドレスから物理アドレスへの変換は、物理メモリの1 KiBページへのページングもサポートする統合 メモリ管理ユニットによって処理されました。 FおよびC Wの 2 ビット (ビット #15 Extended / Compactおよび #10 Linear / Segmented ) を使用して、3 つのアドレッシング形式を選択できます。

- コンパクト: Z8000 の非セグメント モードと同等の16 ビットで64 KiBの均一アドレス空間

- セグメント化: セグメント サイズの指定に論理アドレスの上位ビットが使用されたため、 4 GiBではなく2 GiB x 32 ビットのセグメント化されたアドレス空間。

- または16 ビットディスプレイスメントの64 KiBの 32,768 セグメント

- または24 ビットの動きを持つ16 MiBの 128 セグメント

- Linear : 均一な4 GiB 、 32 ビットのアドレス空間

- レジスタ バンクには、メモリ内のアキュムレータ、インデックス、またはポインタとして使用できる 16 個の32 ビット汎用レジスタが含まれています。他の 2 つのレジスタ ( FPとSP 、それぞれフレーム ポインタとスタック ポインタ) は、C、E、E、および R 命令によるプロシージャ呼び出しを連鎖するために使用され、 32 ビットレジスタは命令ポインタとして使用され、 16 ビットレジスタには命令ポインタが含まれていました。マシン ステータス ワードとバイナリ フラグ ( FおよびC W )。割り込みとトラップ中に暗黙的に保存されます。他の 9 つの特殊レジスターは、プロセッサーの状態、システム構成、およびメモリー管理を制御するために使用されました。

- 16 個の32 ビット汎用レジスタ (RR0、RR2.. RR28、RR30) は、8 つの64 ビットレジスタ (RQ0、RQ4.. RQ24、RQ28) としてアクセスできます。最初の 8 つの32 ビット汎用レジスタ (RR0、RR2.. RR12、RR14) は、最初の 8 つ (R0、R1.. R6 を含む) を含む 16 の16 ビットレジスタ (R0、R1.. R14、R15) としてアクセスすることもできます。 、R7 ) は、16 個の8 ビットレジスタ (RH0、RL0、RH1、RL1.. RH6、RL6、RH7、RL7) としてアクセスできます。

- 16 個の16 バイトブロックに構造化された256 バイトの連想キャッシュがプロセッサ回路に統合され、命令とデータの両方のレベル 1 キャッシュとして機能しました。

- E P A は、特に Zilog Z8070 浮動小数点計算ユニットを管理するように設計されています。